Förderjahr 2022 / Projekt Call #17 / ProjektID: 6274 / Projekt: fast_open_switch

Das Zusammenspiel von Hard- und Software muß bei einem elektronischen Geräte gewährleistet sein. Wird beides gleichzeitig entwickelt wird, braucht es für die Softwareentwickler eine Hardware-Zwischenlösung .

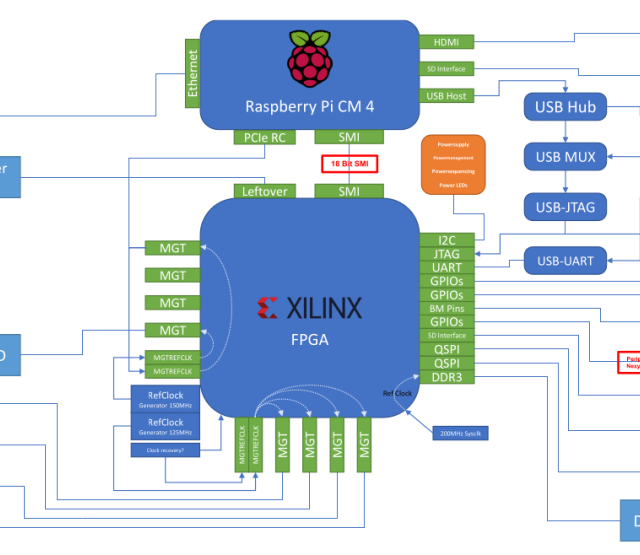

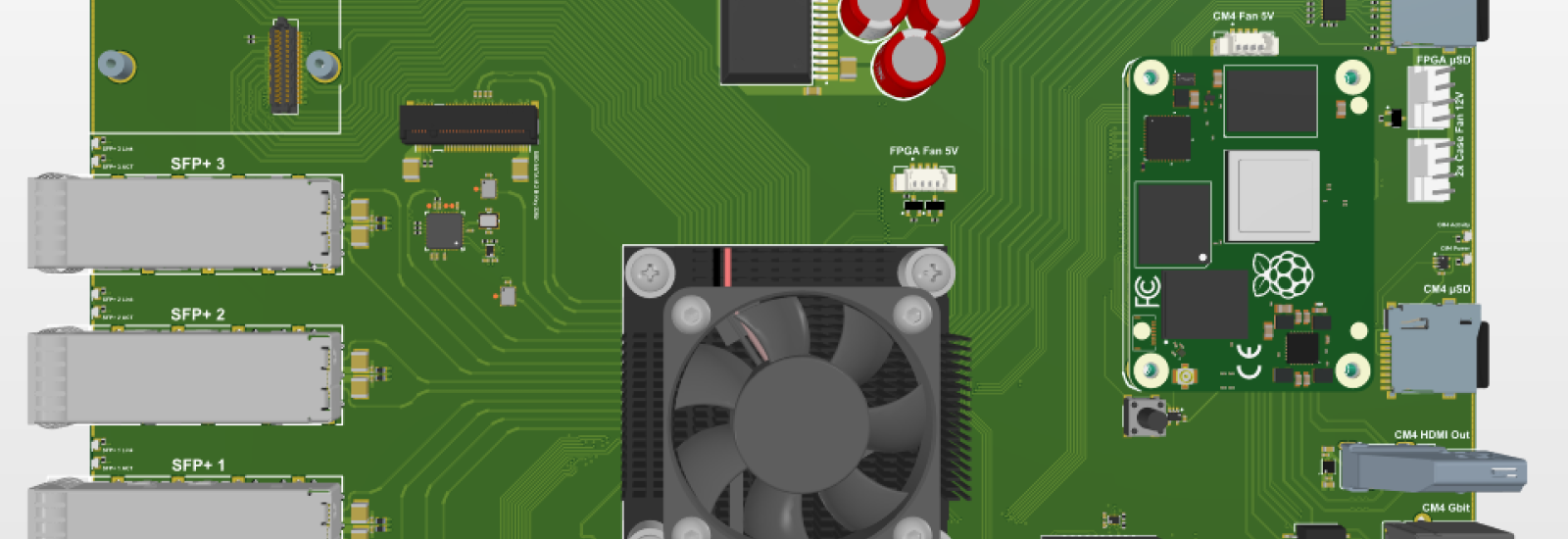

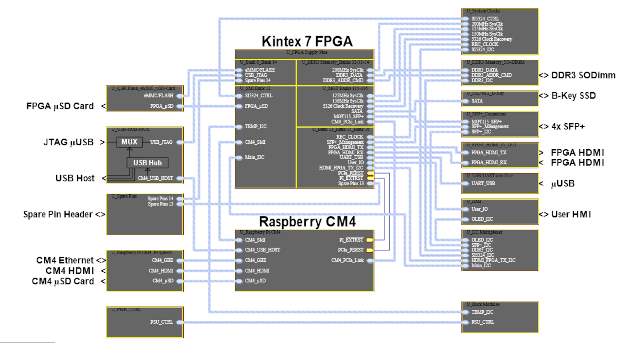

Mitte Jänner 2023 hatte sich das Entwickerteam auf die detailierte Hardware-Architektur geeinigt. Es wurde viel Wert auf maximale Flexibilität gelegt sodaß Forscher und Unternehmen ihre Produkte auf dieser Hardware aufbauen können.

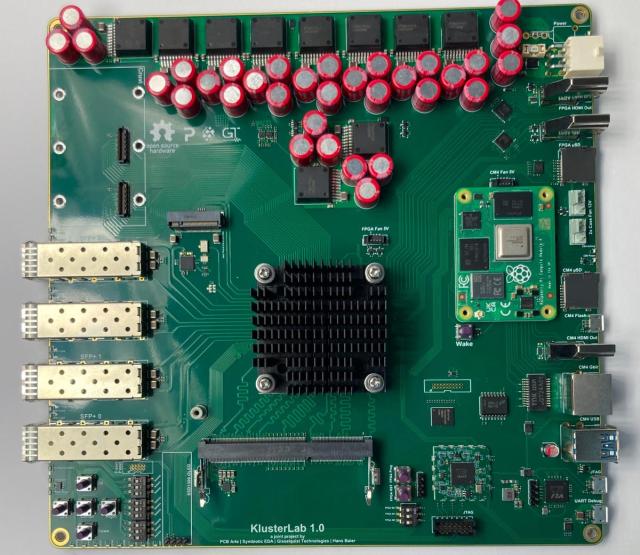

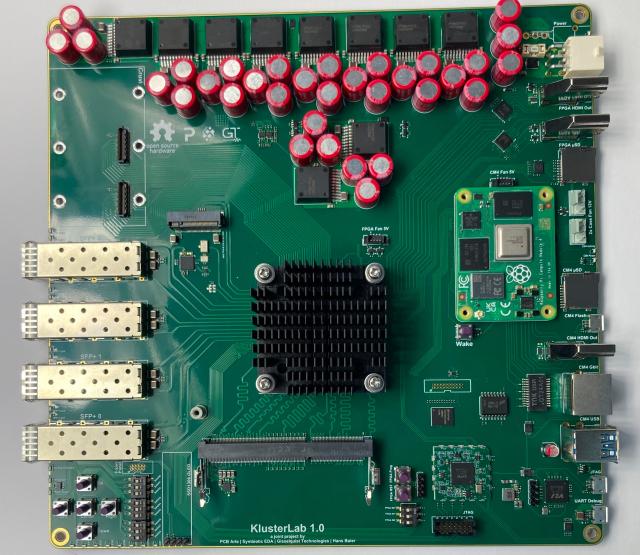

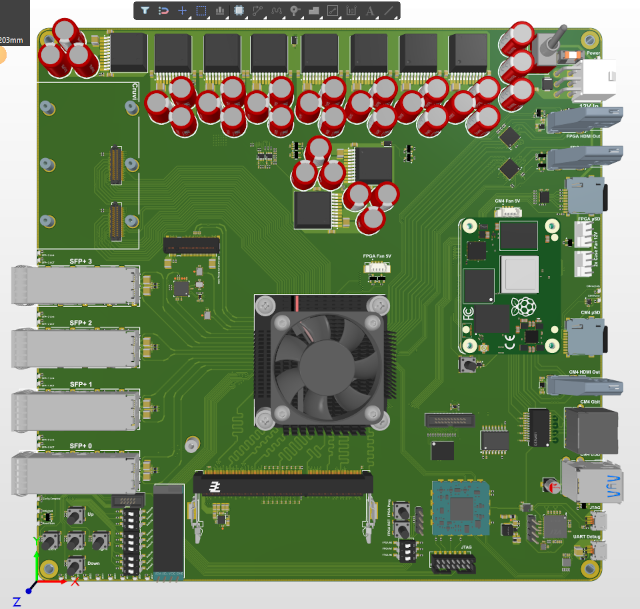

Im März wurde nun das Board-Design fertig gestellt und demnächst produziert. Alle Bauteile wurde bereits beschafft sodaß einer Bestückung des ersten Prototyp nichts im Wege steht.

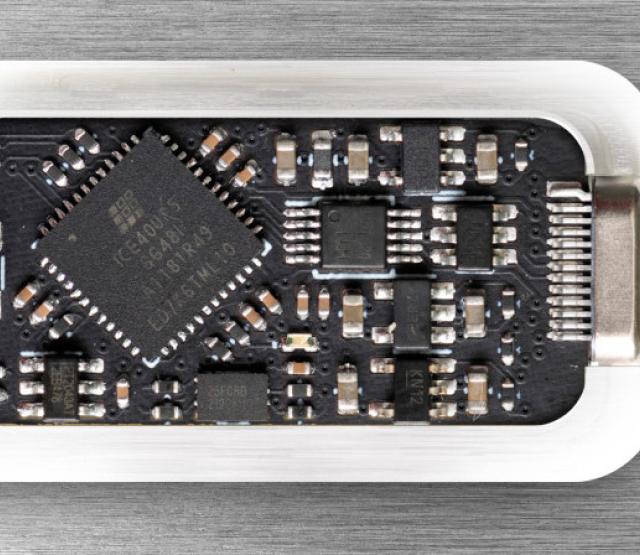

Vor der Entwicklung des Boards wurde noch eine Adapterplatine zwischen FPGA und Management CPU entwickelt, die dem Softwareentwickler es ermöglicht, frühzeitig seine Software zu testen.

Die Adapterplatine wurde produziert und ist bereits im Einsatz.

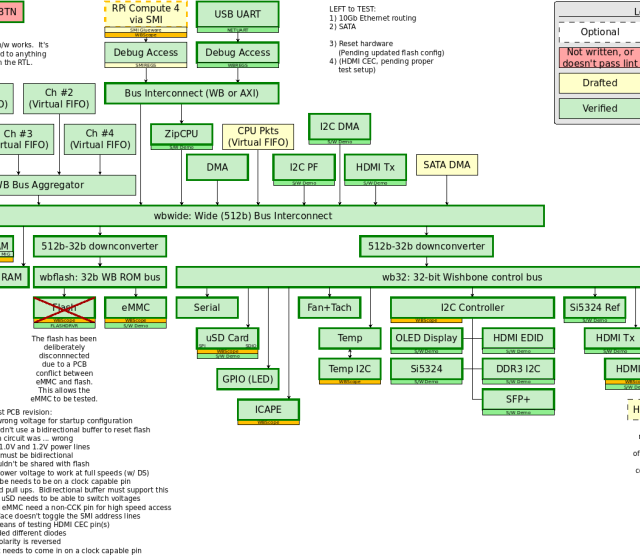

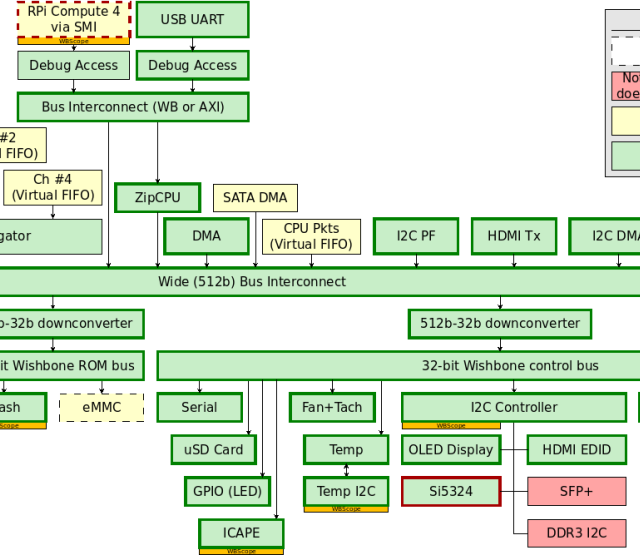

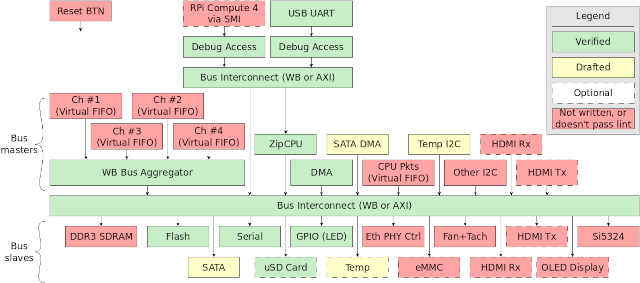

Auch wurde mit der Entwicklung und Verifikation der FPGA Gateware in Verilog begonnen, die die Funktion des Ethernet Switches bestimmt. Im Laufe des Jahres werden die noch zu entwickelnden Lücken gefüllt werden. Vor allem die Entwicklung des schnellen DDR3 memory controller wird erheblichen Aufwand verursachen. Eine Besonderheit dieses Design ist der mit 512 Bit extrem breite Bus, der alle Komponenten auf dem FPGA verbindet. Eine weitere Besonderheit ist der Bus Aggregator, der die Speicherzugriffe auf den DDR3 Speicher für alle Ethernet Kanäle bündelt. Damit kann der durch das DDR3 Speicher-Interface verfügbare Datendurchsatz für das Zwichenspeichern von Datenpaketen voll ausgenutzt werden.

Edmund Humenberger