Förderjahr 2022 / Projekt Call #17 / ProjektID: 6274 / Projekt: fast_open_switch

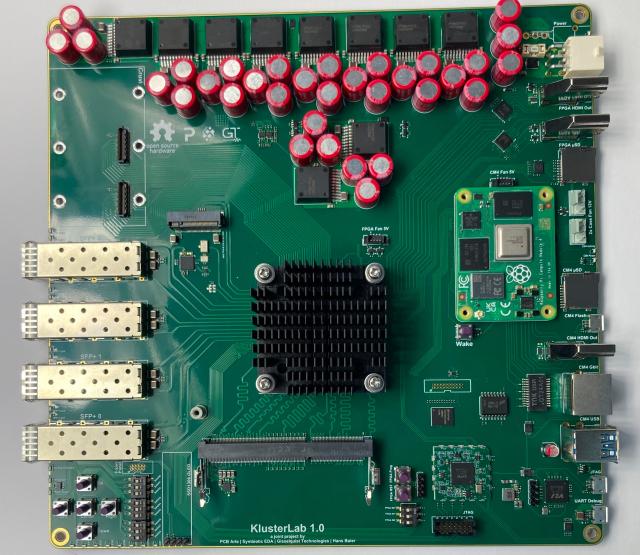

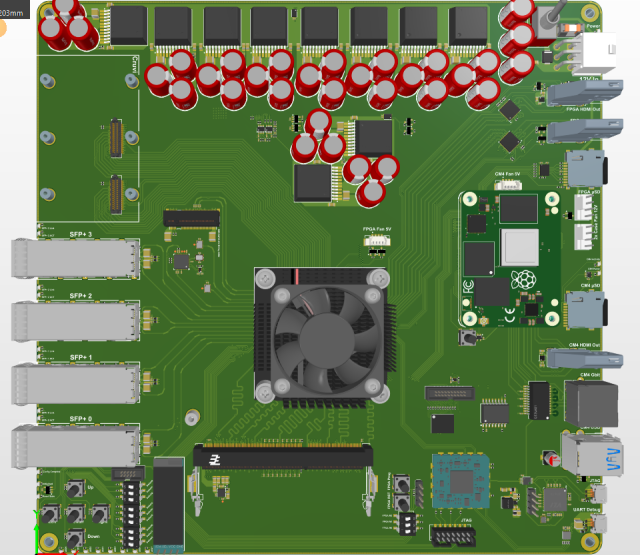

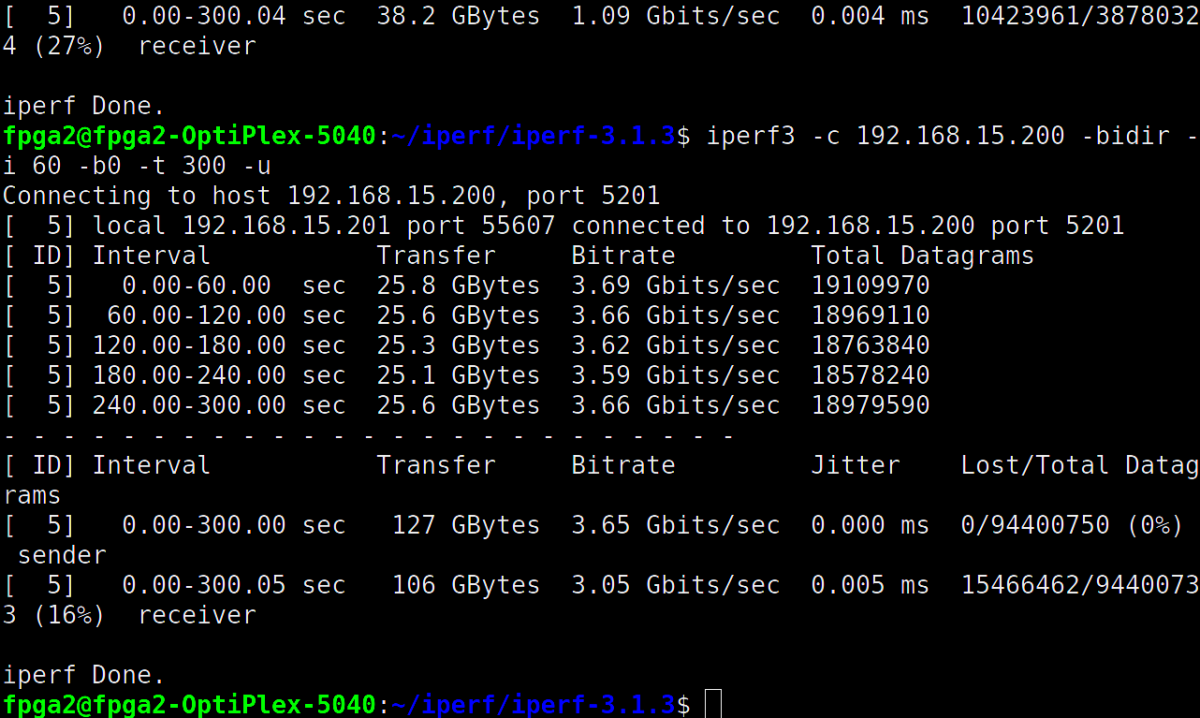

You never know until you measure. We measured with iperf a thoughput of 3.6 Gbit/sec in any direction on our 4-port switch. This means that we demonstrated the transfer of IP packets of any size to and from the DDR3 memory at a speed of 7 Gbit/sec.

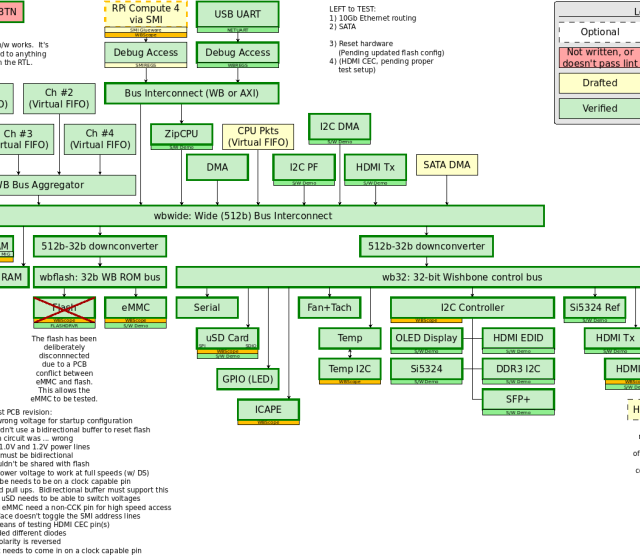

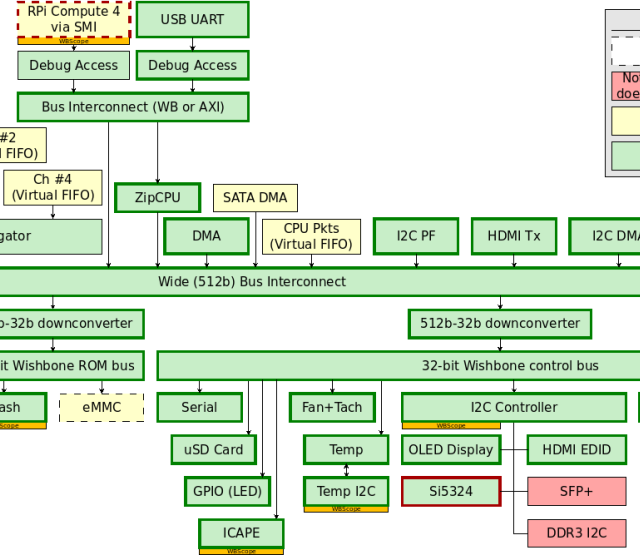

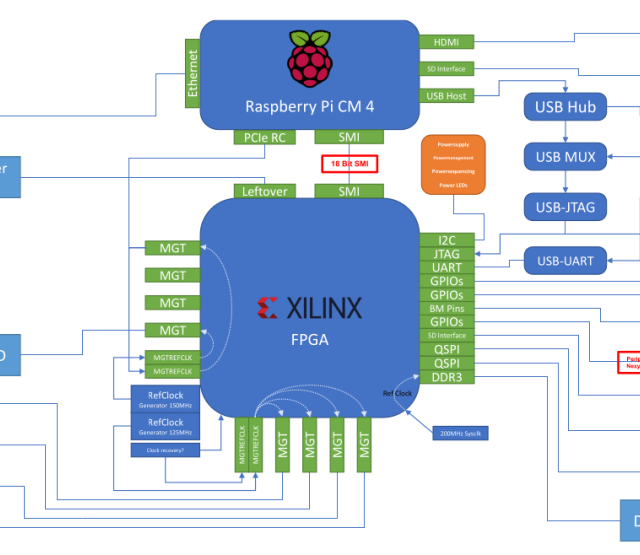

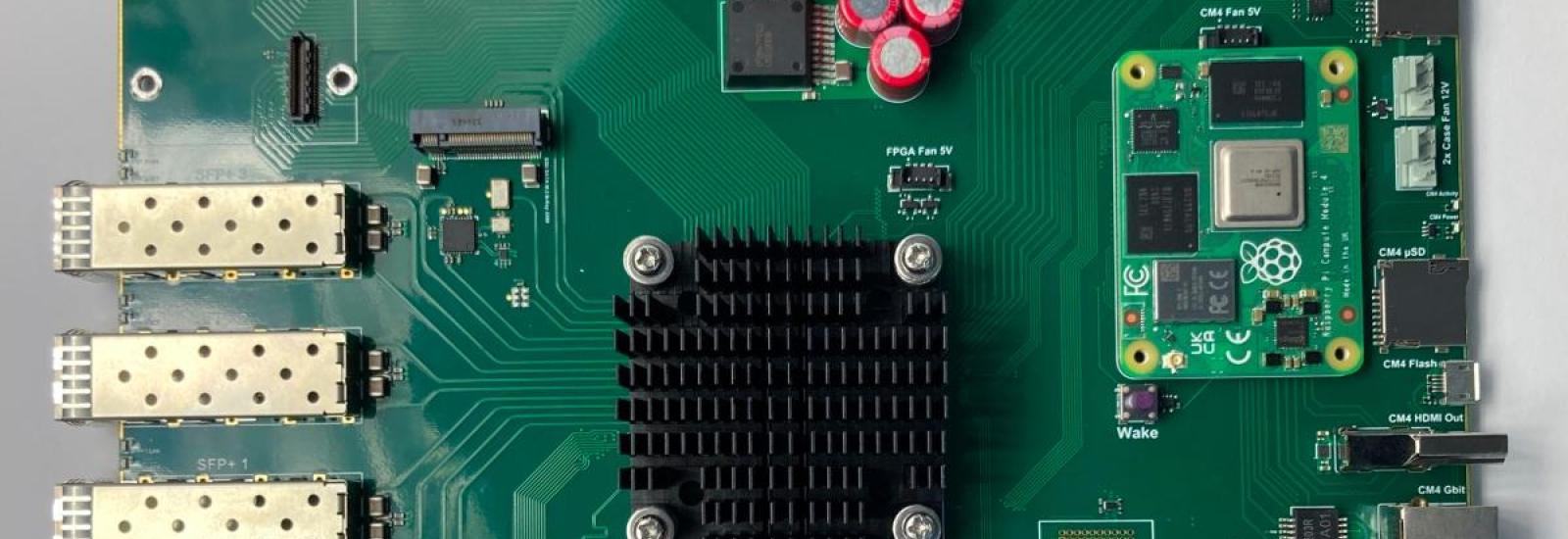

This performance is not the upper limit as every Ethernet connector of our switch can transfer data with up to 10 Gbit/sec. So there is some room left for improvement. Our DDR3 memory controller was designed to handle 50Gbit/sec. To achieve higher throughput speeds would require a detailed analysis of our current full data pipeline design (see graphic below) in operation do identify each speed bottleneck. This would require the impementation of performance counters and other instrumentation of the gateware design which in this project we did not have the ressoures for.

Even as the hardware we have built due to cost constraints is only is a 4 port switch, there is a lot of possible ways for a data packet to travel though the switching fabric. We did measure the speed on any of the routes.

Every data packed needed to go thought the full Ethernet data pipeline in the FPGA. The challenge is that we have to apply different clock speeds in the different areas. All buffers should stay relatively empty so that no unneccesary latency is generated or worse packets get dropped becasue a buffer is full. A lot of IP blocks had been implemented and verified by formal methods and by simulation.

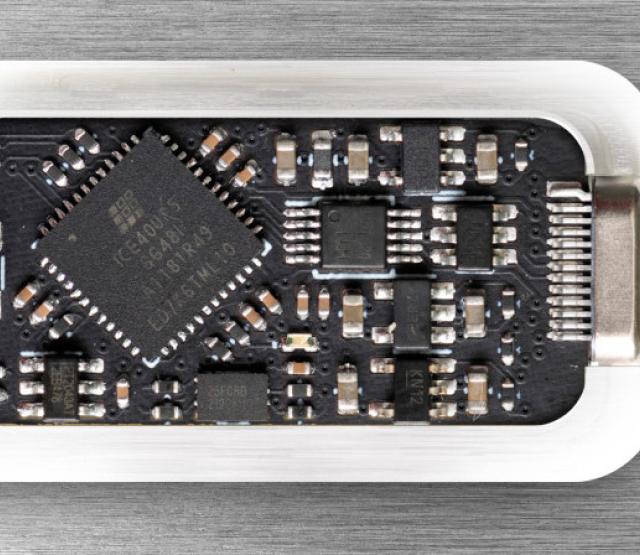

During the project, a massive amount of gatware was developed.

The project was a full success and we hope that many elements of this project will be reused by others for other projects or the switch will be used as a basis for further development of more advanced functions like hardware accelerated and secured VPN.

We are looking forward to improve the switch to make it faster and easier to use.

Edmund Humenberger