Förderjahr 2022 / Projekt Call #17 / ProjektID: 6274 / Projekt: fast_open_switch

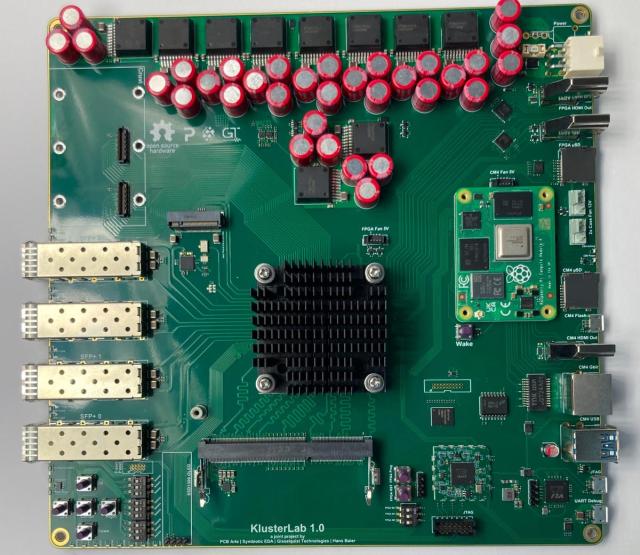

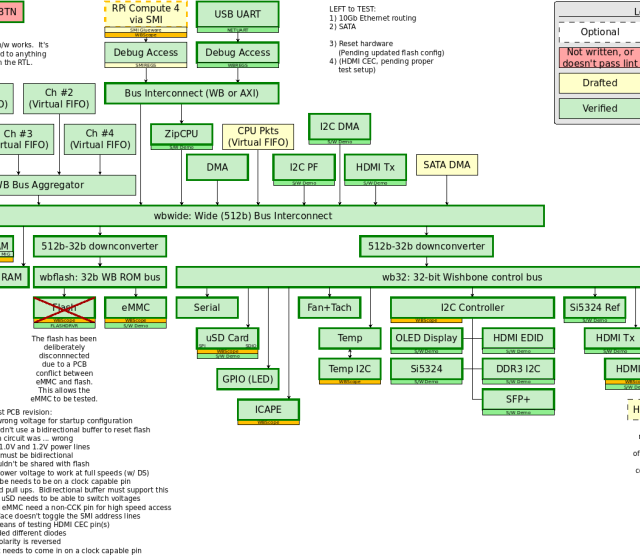

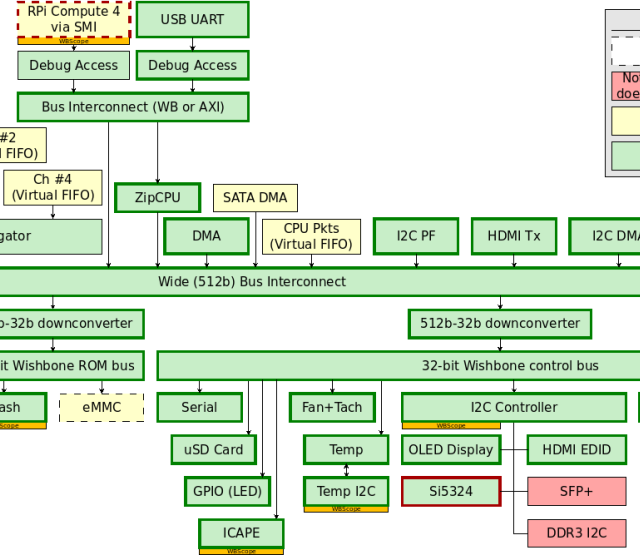

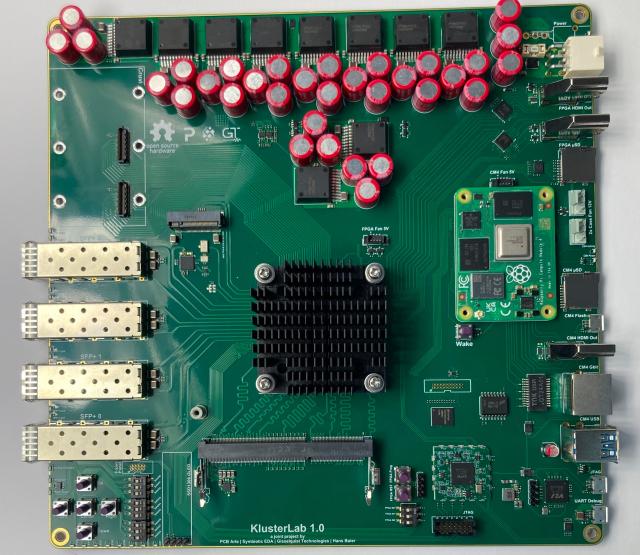

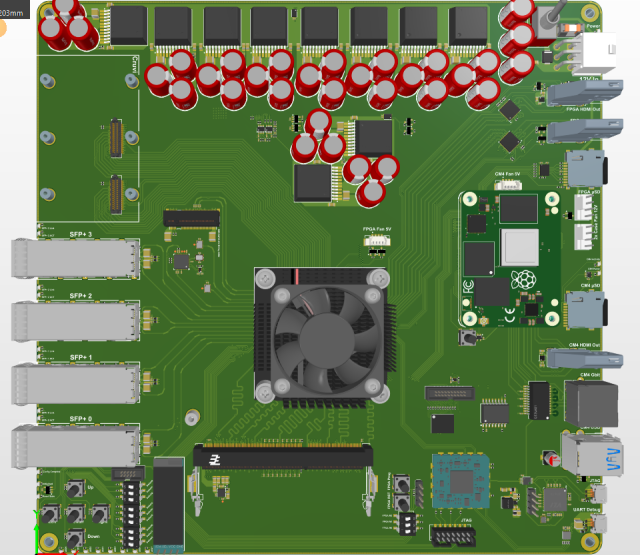

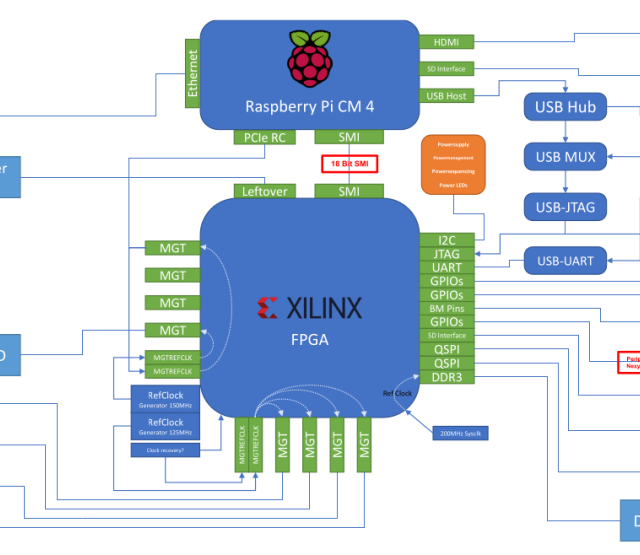

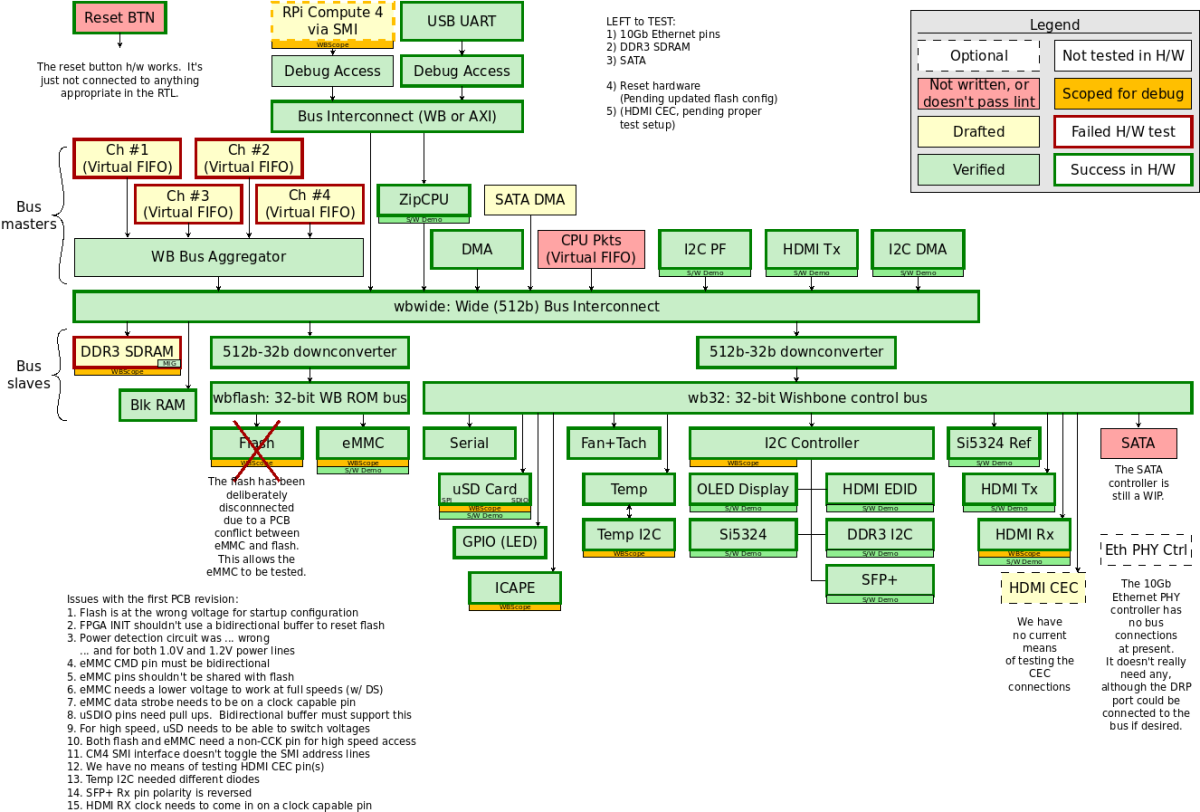

A switch consists of many functional blocks to be able to forward data packets. The architecture picture shows what blocks we had to implement and in what development stage they currently are. We are in the final stretch.

The red marked virtual FIFO is needed to store all the incoming packets before they are forwarded. This buffer makes sure that no data packets have to be dropped when an outgoing data channel is already used at full capacity. For those who want to dive deep into the details of its design, please read the blog article about it. We could not yet test the FIFO as the availability and function of the DDR3 memory controller is a requirement for this.

Special in our design is the 512bit wide data bus. This is required to handle the massive data throughput provided by the 10Gbit Ethernet connections. Internally a FPGA does only work with 100MHz, which means that at least 100 bit need to be handled at a time. But that would not lead and time for doing processing on the data packets. Therfore we had to go to 512 bit wide data busses. We already tested the interaction between the switch hardware and a PC with a 10 GBit Ethernet card and could achieve data synchronisation.

We already tested the interaction between the switch hardware and a PC with a 10 GBit Ethernet card and could achieve data synchronisation.

As an additional gimmic did we integrate a SATA connector on the switch, but we will not develop the required gateware or software to use the solid state hard disk. The same is true for the emmc storage device.

We also added hardware for HDMI-in and verified its function. With the right gateware, the board could be used as remotely managed Internet video streaming device.

Edmund Humenberger