Förderjahr 2022 / Projekt Call #17 / ProjektID: 6274 / Projekt: fast_open_switch

Fortschritt ist langsam aber stetig

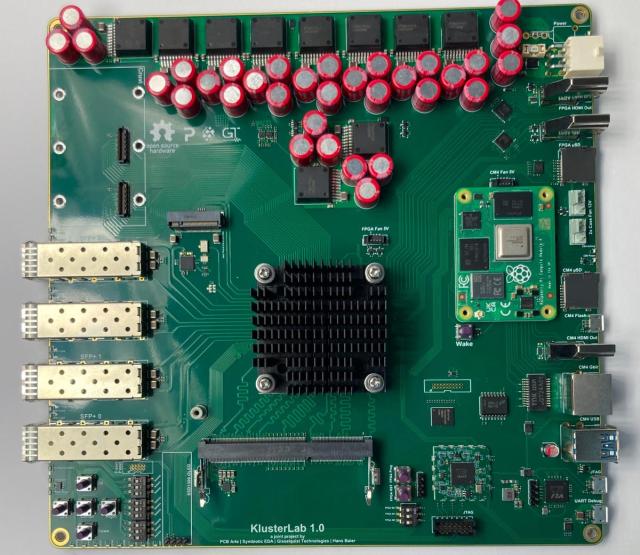

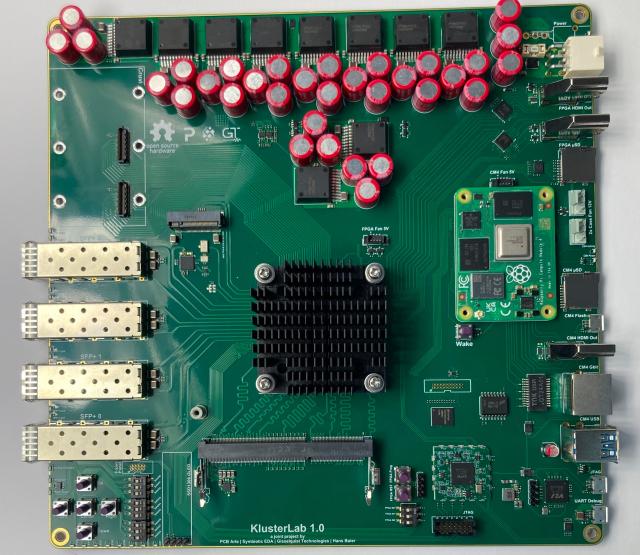

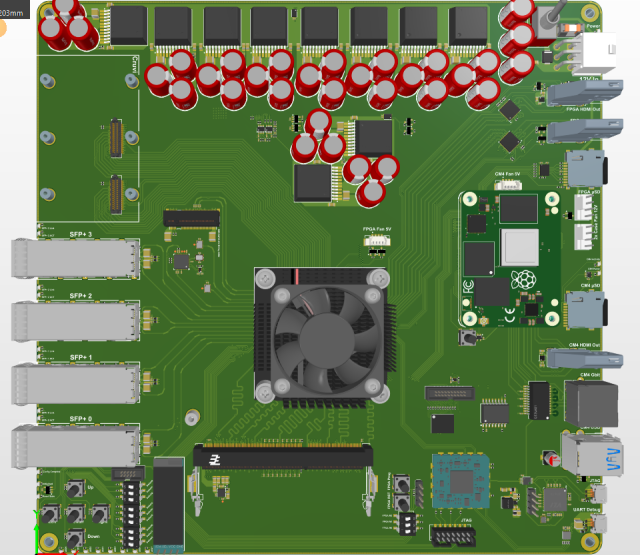

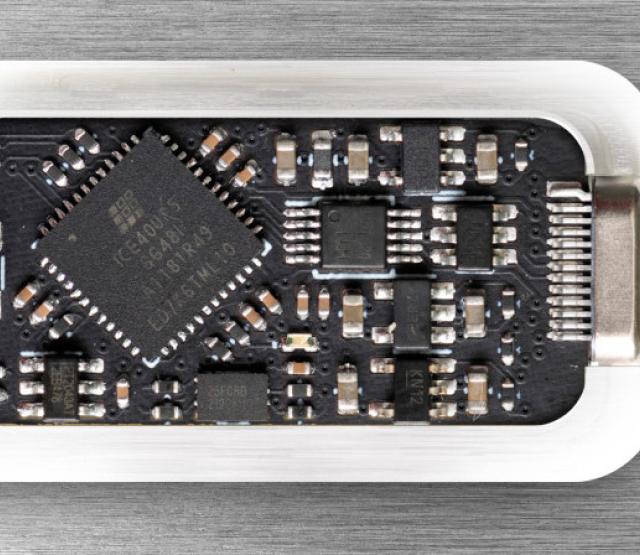

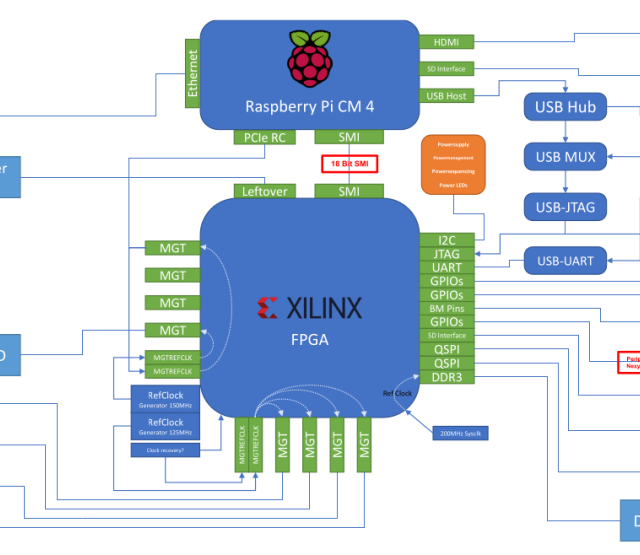

Für das Testen verschiedenster Hardware Komponenten, die auf dem FPGA verbaut sind, wurde das Board in ein Test Setup eingefügt. Eine FPGA Konfigurationdatei kann über den RaspberryPI auf das Board geladen werden.

Damit ist das remote Testen möglich. Der HDMI output funktioniert bereits. Wie im Bild zu sehen ist funktioniert auch das OLED display. Ein HW Designfehler wurde bei der Anbindung der SD-Card entdeckt, der nur in einer neuen Boardversion behoben werden kann.

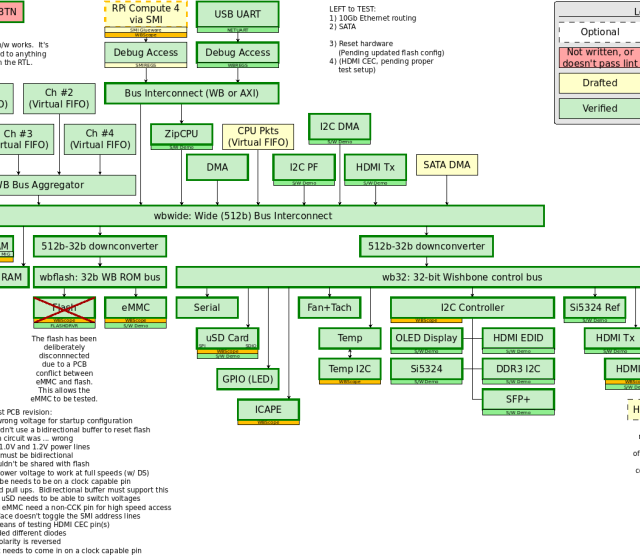

Das Testen der 10 Gbit Ethernet Implementierung sollte in den nächsten Wochen starten können. Als erstes wird ein einfaches port forwarding implementiert, welches den beiden Testrechnern erlaubt, über den Switch miteinander zu kommunizieren. Damit können wir zeigen, dass die 10 Gbit Ethernet synchronisation, das packet decoding und encoding einwandfrei funktionieren.

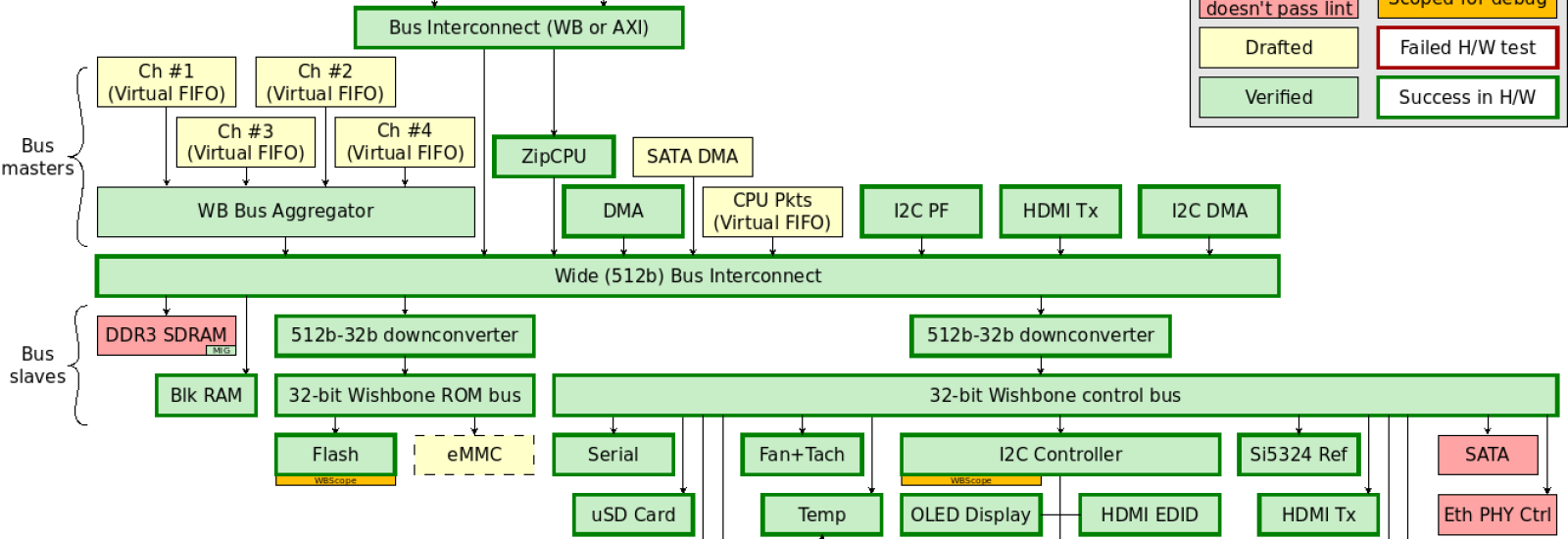

Dabei wird der 512 Bit breite interne Datenbus von der DMA Engine gesteuert. Der 512 bit breite Datenbus ist notwendig, damit zwischen den 10 Gbit schnellen Ethernet Schnittstellen die Daten ohne Stau ausgetauscht werden können.

Ein weiteres großes Entwicklungsprojekt ist der DDR3 Speichercontroller, welcher demnächt für einen ersten Funktionstest bereit sein sollte. Die Zielsetzung des Speicherconroller ist, die durch das DDR3 Hardware gegebene 32 bit breite Speicherinterface zur Verfügung stehende Datenbandbreite bei der gegebenen Taktrate von 400 MHz so gut wie möglich nutzen zu können.

Das aktuelle Switch Design ist auf github zu finden

Edmund Humenberger