Förderjahr 2022 / Projekt Call #17 / ProjektID: 6274 / Projekt: fast_open_switch

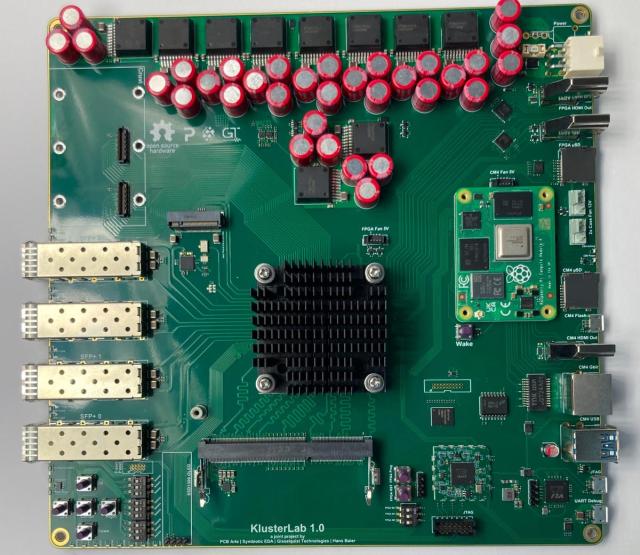

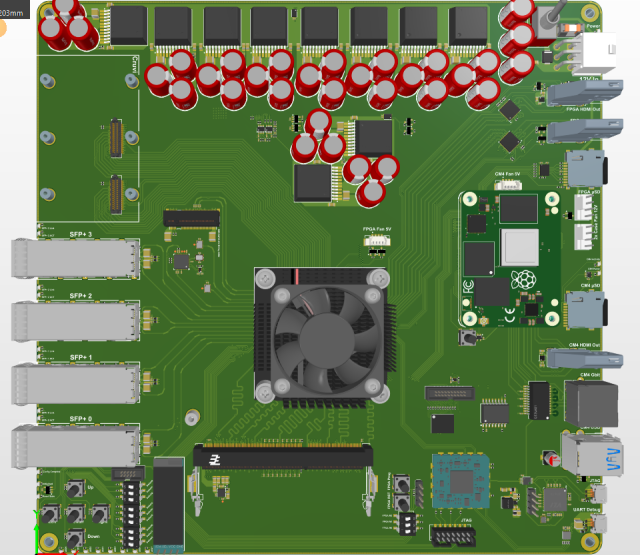

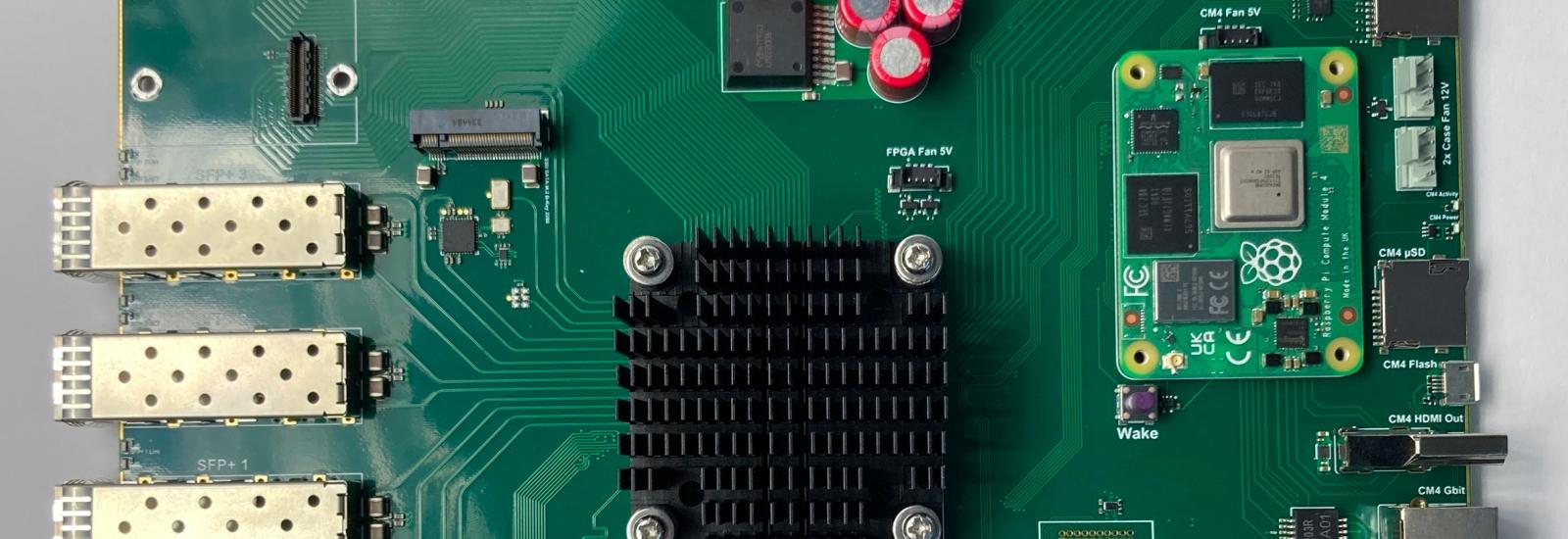

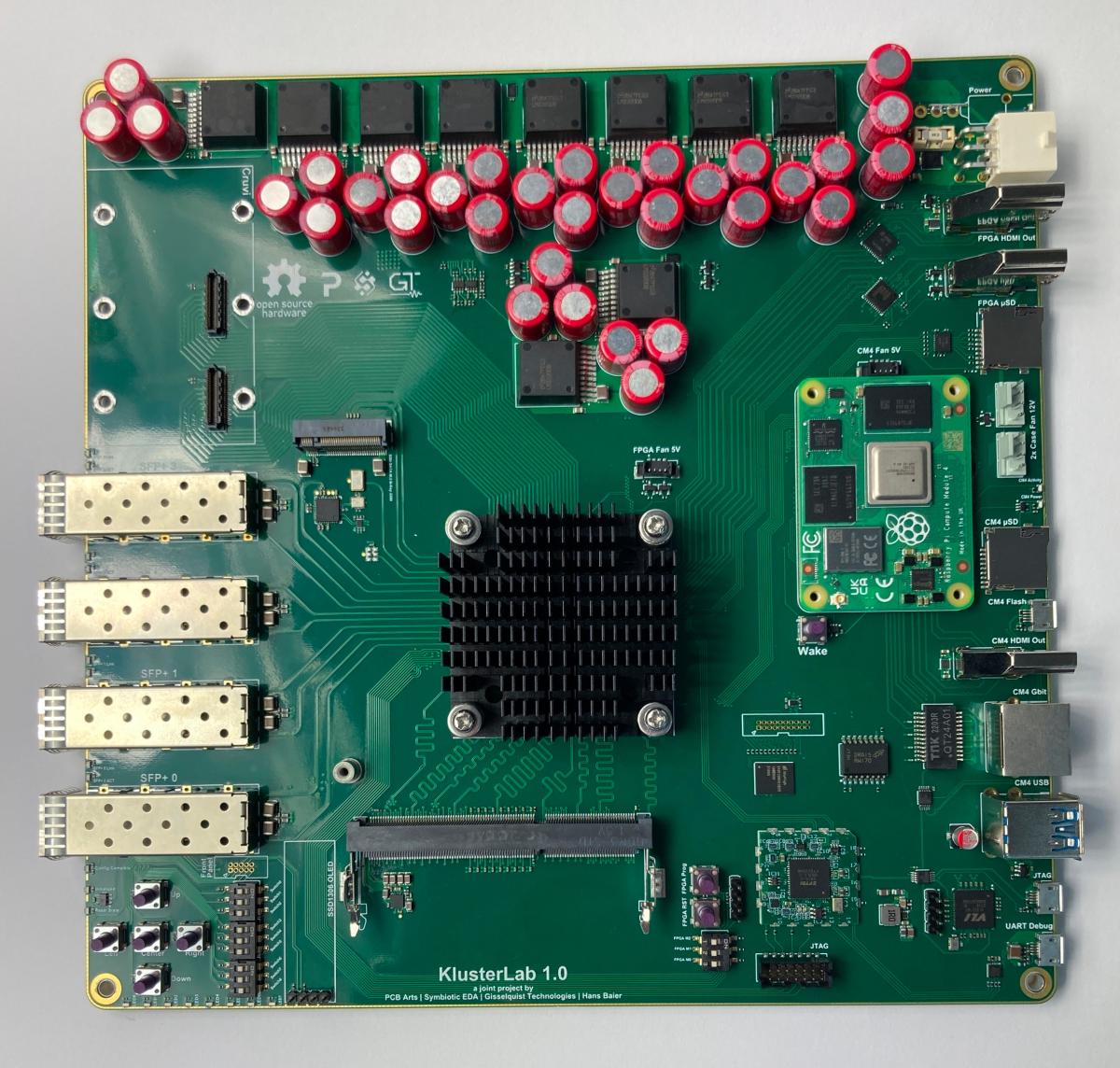

Im April haben wir eine erste Version der von uns entworfenen Switch Hardware aufgebaut und in Betrieb genommen. Das Hochladen von Designs in den FPGA funktioniert und nun werden wir die restlichen auf dem Board verbauten Komponenten testen.

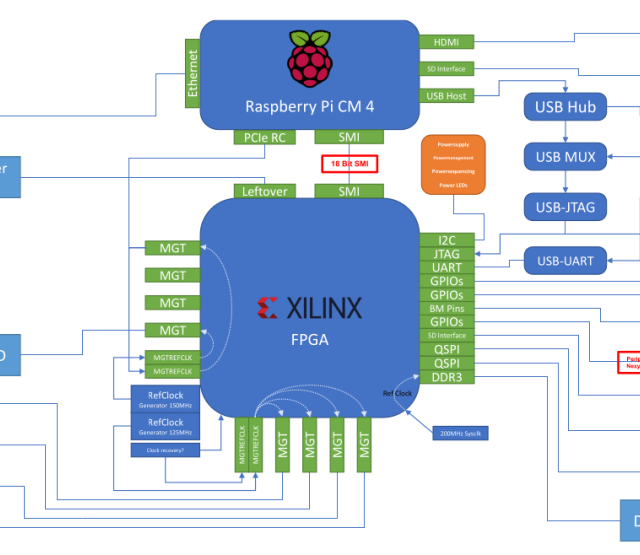

Der Zugriff auf das Ethernet Switch board ist per Ethernet vom CM4 RaspberryPi Modul aus möglich und funktioniert bereits. Damit kann das Hochladen von Gateware auf den FPGA zum Testen der von uns derzeit entwickelten Switch Funktionalität aus der Ferne vorgenommen werden.

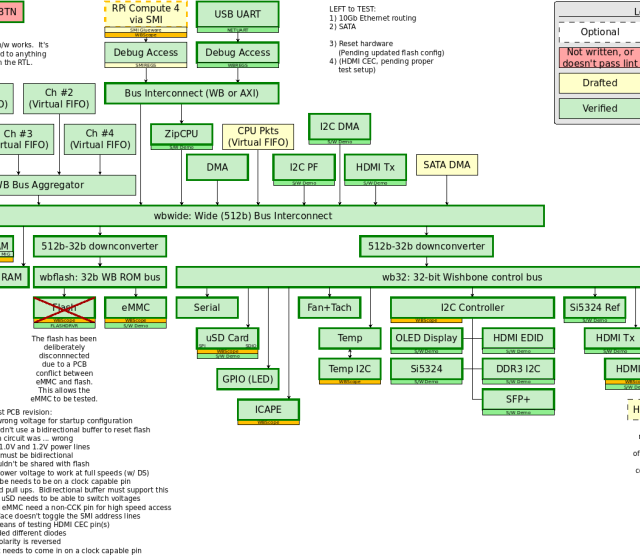

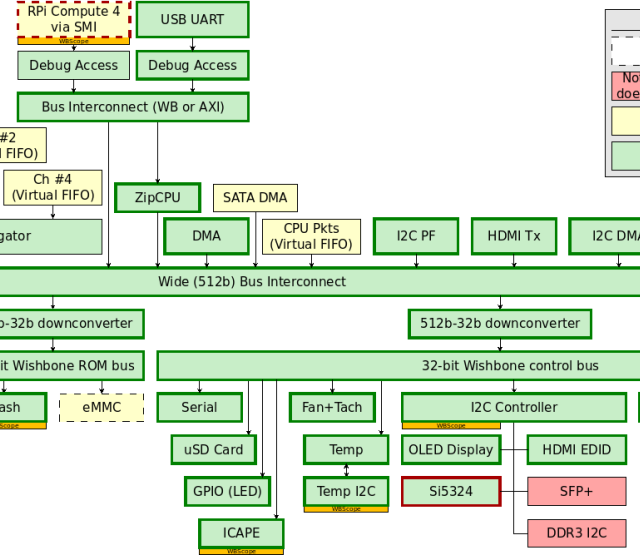

Derzeit entwicklen wir die notwendige Gateware zur Anbindung des FPGA über 10Gbit Ethernet. Dazu implementieren wir den gesamten Ethernet 10 Gbit Standard in Verilog. Es ist notwendig, empfangene IP Datenpakete mit voller Geschwindigkeit in den DDR3 Speicher schreiben zu können als auch zur gleichen Zeit mit voller Geschindigkeit gleichzeitig Datenpakete aus dem DDR3 Speicher lesen zu können. Dies erfordert einen hochperformanten Speichercontroller, der mit einem 512 bit breiten Datenbus an die vier 10 Gbit schnellen Ethernet Schnittstellen angebunden ist.

In den kommenden Wochen werden wir die korrekte Funktion der Speicheranbindung verifizieren und die Performance testen.

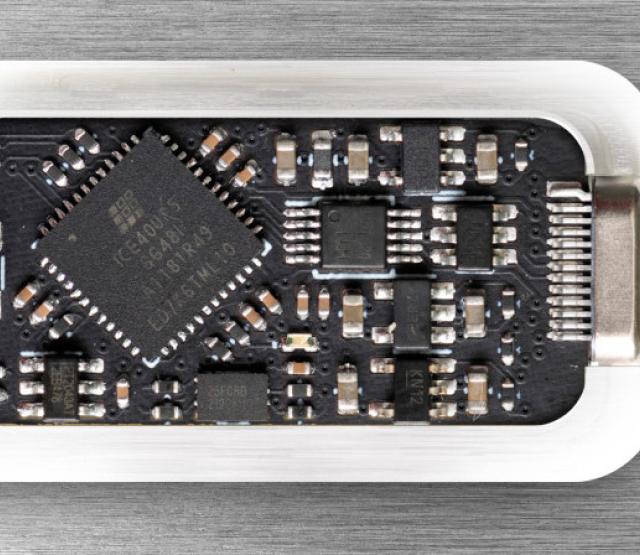

Zusätzliche Schnittestellen können über die CRUVI Hochgeschwindigkeitsstecker an das Board angebunden werden. Dieses Board ist das erste welches eine derartige flexible Datenschnittstelle mit einer Datenübertragungsrate von 40Gbit pro Stecker anbietet. Dies kann für das Anbinden von Radio- oder Videosensoren verwendet werden.

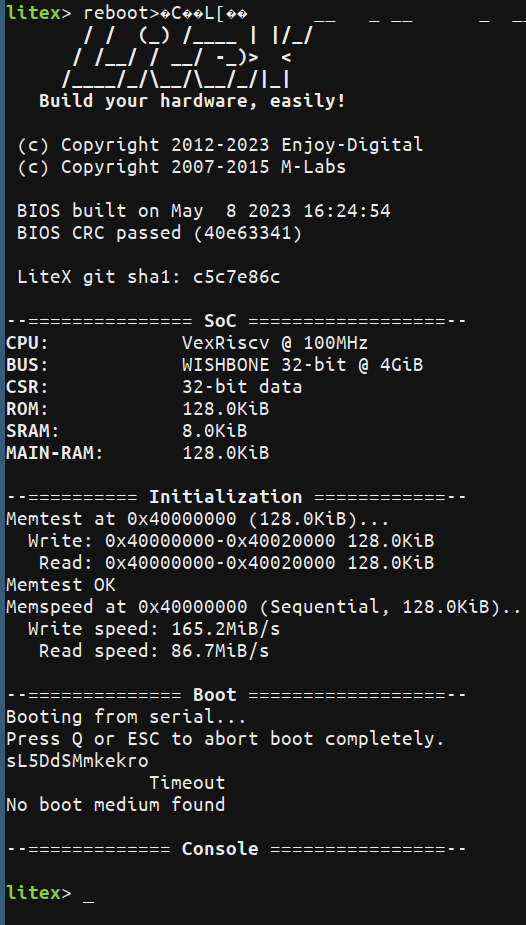

Als erstes konnten wir einen 32 bit RISC-V Prozessor in den FPGA hochladen, der uns bei der Verifikation der Anbindung des DDR3 Speichers nützlich sein wird. Wir werden mit diesem Prozessor auch eine 1 GBit Ethernet Verbindung validieren.

Edmund Humenberger